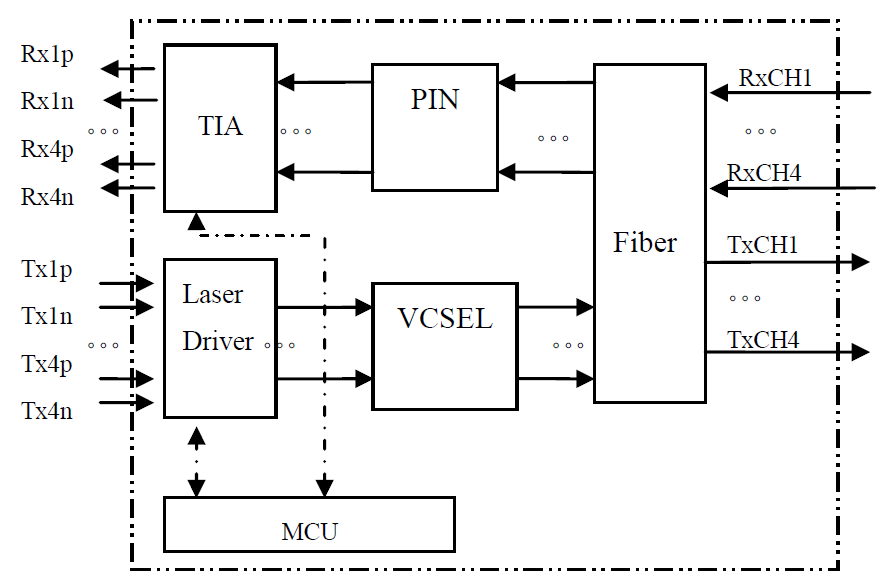

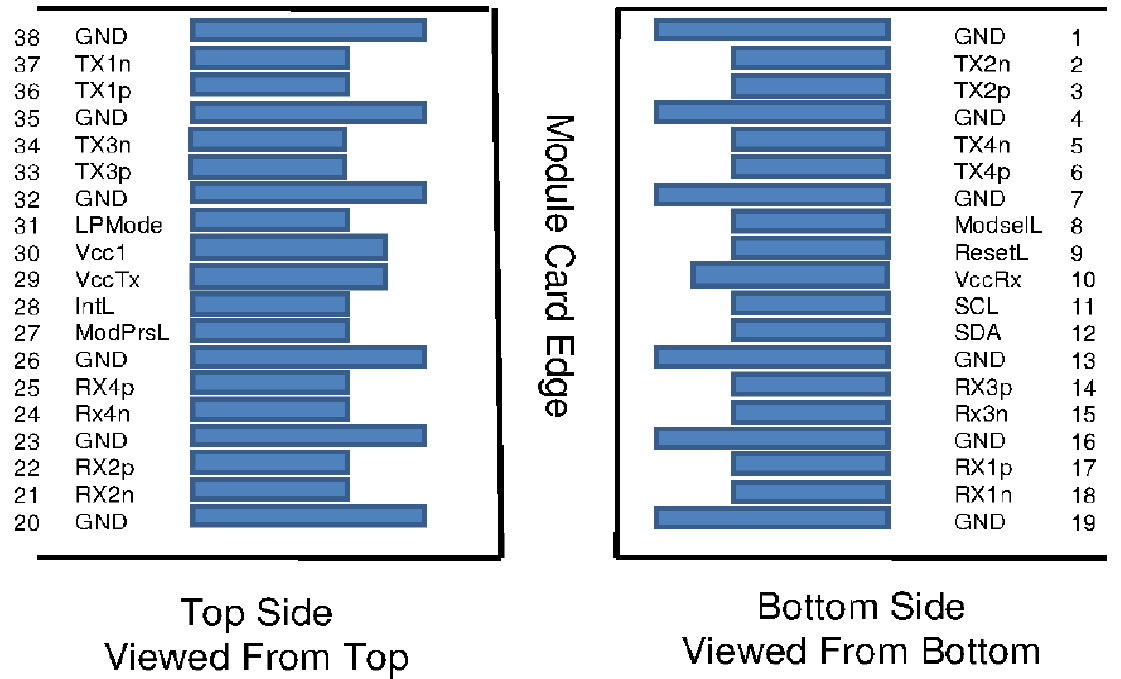

HANSUN Communication HX-QSFP28-AOC1M is a Four-Channel, Pluggable, Parallel, Fiber-Optic 40G QSFP+ SR for 100 or 40 Gigabit Ethernet, Infiniband FDR/EDR Applications. This transceiver is a high-performance module for short-range multi-lane data communication and interconnects applications. It integrates four data lanes in each direction with 100 Gbps bandwidth. Each lane can operate at 25Gbps up to 70 m using OM3 fiber or 100 m using OM4 fiber. These modules are designed to operate over multimode fiber systems using a nominal wavelength of 850 nm. The electrical interface uses a 38 contact edge type connector. The optical interface uses a 12 fiber MTP(MPO) connector.

Applications of 100G QSFP28 AOC

- IEEE 802.3bm 100GBASE SR4 and 40GBASE SR4 28G Fiber Channel

- Infiniband FDR/EDR

Specifications of 100G QSFP28 AOC

Absolute Maximum Ratings

| Parameter | Symbol | Min | Max | Unit |

| Storage Temperature | HX | -20 | 85 | ℃ |

| Case Operating Temperature | TCase | 0 | 70 | ℃ |

| Relative Humidity | RH | 0 | 85 | % |

| Supply Voltage | VCC | -0.5 | 3.6 | V |

Recommended Operating Conditions

| Parameter | Symbol | Min | Typical | Max | Unit |

| Case Operating Temperature | TCase | 0 | – | 70 | ℃ |

| Humidity | RH | 5 | – | 85 | – |

| Supply Voltage | VCC | 3.13 | 3.3 | 3.47 | V |

| Data Rate Per Lane | DR | – | 25.78125 | – | Gbit/s |

| Fiber Bend Radius | Rb | 3 | – | – | cm |

Electrical Characteristics

NOTE: The EDR module requires an electrical connector compliant with SFF-8662 or SFF-8672 be used on the host board to guarantee its electrical interface specification. Please check with your connector supplier

| Parameter | Symbol | Min | Typical | Max | Unit |

| Supply Voltage | VCC | 3.15 | – | 3.45 | V |

| Supply Current | ICC | – | – | 1010 | mA |

| Total Power Dissipation1,2 | P | – | – | 3.5 | W |

| Transmitter | |||||

| Differential Input Voltage | Vin | – | – | 900 | MVP-p |

| Differential Termination Resistance Mismatch | – | – | – | 10 | % |

| Transition Time, 20 to 80% | Tr, Tf | 10 | – | ps | |

| Receiver | |||||

| Differential Output Voltage | Vout | – | – | 900 | MVP-p |

| Differential Termination Resistance Mismatch | – | – | – | 10 | % |

| Transition Time, 20 to 80% | Tr, Tf | 9.5 | – | – | ps |

| Bit Error Rate3 | BER | – | – | 10-12 | – |

Note:

- Maximum total power value is specified across the full temperature and voltage range

- Settable in various discrete steps via the I2C interface

- BER=10-12, PRBS 231-1@25.78125Gbps

HANSUN

HANSUN